# A New Low Power Single Bit Full Adder Design with 14 Transistors using Novel 3 Transistors XOR Gate

Manoj Kumar, Sandeep K. Arya, and Sujata Pandey

Abstract-In present work a new XOR gate using three transistors has been proposed. Design shows adequate output logic levels with noise margin of 2V with 3.3V input signals. XNOR logic, obtained with addition of inverter shows improved noise margin of 3.2V. A new design for single bit full adder has been implemented using proposed XOR/XNOR gates and transmission gate multiplexer. Full adder designed with 14 transistors shows power dissipation of  $655.6149\,\mu\text{W}$  and maximum output delay 0.11055ns. Proposed adder circuit shows adequate noise margin of 3.2 V for Sum (Sum output) and 2.2V for Cout (Carry output) with supply voltage of 3.3V. Circuit works well with reduced supply voltage and simulations have been carried out up to 1.8V supply voltage. Simulations are performed by using SPICE based on TSMC 0.35 µm CMOS technology. Power consumption of proposed full adders has been compared with earlier reported circuits and proposed circuit's shows better performance in terms of power consumptions and transistor count.

*Index Terms*—CMOS, exclusive-OR (XOR), exclusive-NOR (XNOR), full adder design, low power and transmission gate.

## I. INTRODUCTION

Research efforts in the field of low power VLSI (very large-scale integration) systems have increased many folds due to exponential growth of portable electronic devices like laptops; audio/video based multimedia and cellular communication devices. With rise in number of transistors on chip, power consumption of VLSI systems is also raising which further, adds to run time failures and reliability problems. Packaging and cooling mechanism become more complex and costly with excessive power consumption. Low power consumption is one of important design criteria for IC designers at all levels of design along with delay and area considerations. Faithful functionality of device at lowest supply voltage is also vital consideration.

Three major source of power consumption exists in CMOS VLSI circuits: 1) switching power due to charging and discharging of node capacitances, 2) short circuit power due to short current flow from power supply to ground with simultaneous functioning of p-network and n-networks, 3) Static power consumption due to leakage currents.

Power consumption of VLSI circuits can be reduced by scaling supply voltage and capacitance. With the reduction in supply voltage, problems of small voltage swing, insufficient

Manuscript received May 22, 2012; revised June 26, 2012.

noise margin and leakage current starts to instigate.

Addition of two binary numbers is fundamental and most frequently used arithmetic operation in microprocessors, digital signal processors (DSP), and application-specific integrated circuits (ASIC) etc. Single bit binary adders are significant building blocks in VLSI circuits and efficient implementation of these adders will affects the performance of entire system. In recent years different types of adder using various logic styles have been proposed in literature. Standard CMOS 28 transistor adder using pull up and pull-down networks having equal number of NMOS and PMOS transistors is reported in [1]. Complementary pass-transistor logic (CPL) with 32 transistors having better driving capability with high power consumption is reported in [2].Transmission gate CMOS adder (TGA) based on transmission gates with 20 transistors is reported in [3]. Main disadvantage of TGA is that it requires double number of transistors than pass transistor logic for implementations same logic function. A transmission function full adder (TFA) is based on transmission function theory and used 16 transistors [4]. Multiplexer based adder (MBA) using 12 transistors with elimination of direct path to power supply reported in [5]. Static energy recovery full (SERF) adder with 10 transistors with reduced power consumption at the cost of large delay is presented in [6]. Another design with 10 transistors full adder by using XOR/XNOR gates also reported in [7]. A hybrid CMOS logic style adder with 22 transistors is reported [8]. In [9] a full adder using 22 transistors based on hybrid pass logic (HPSC) is presented. Full adder for embedded applications using three inputs XOR is reported in [10]. In [11] a 16 transistor full adder cell with XOR/XNOR, pass transistors and transmission gate is reported. The function of full adder is based on following two equations, A, B, C<sub>in</sub> are the three single bit inputs and generates two outputs of single bit Sum and  $C_{out}$ , where:

$$Sum = (A \oplus B) \oplus C_{in} \tag{1}$$

$$C_{out} = A.B + C_{in}(A \oplus B) \tag{2}$$

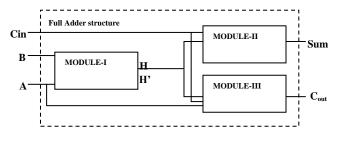

Structured approach for implementation of single bit full adders [12] using XOR/XNOR is shown in Fig. 1. With decomposition of full adder cell into smaller cells, equations (1) and equations (2) can be rewritten as

$$Sum = H'xnorC_{in} = H.C_{in}' + H'C_{in}$$

(3)

$$C_{out} = AH' + C_{in}H \tag{4}$$

where H is half sum (AxorB) and H' is complement of H.

Dr. Sandeep K. Arya is with the Department of Electronics & Communication Engineering, Guru Jambheshwar University of Science & Technology, Hisar, India (e-mail: arya1sandeep@rediffmail.com).

Dr. Sujata Pandey is with the Department of Electronics & Communication Engineering, Amity University, Noida, India (e-mail: spandey@amity.edu).

Fig. 1. Structure of single bit full adder

A large number of reported full adder circuits have been implemented with XOR/XNOR gates and performance of these XOR/XNOR gate also affects the performance of adder circuits. The exclusive-OR (XOR) and exclusive-NOR (XNOR) gates are the basic building blocks of full adder circuits. The XOR/XNOR gate can be implemented using AND, OR, and NOT gates but shows high redundancy [1]. Optimized designs of these gates will certainly improve the performance of VLSI systems as these gates are used as sub block in larger arithmetic circuits. XNOR/XOR designs with reduced number of transistors having adequate performance levels are extremely useful for efficient implementation of the large system such as adders, multipliers etc. XOR gates based on eight transistors and six transistors have been used in [1], [13]. Four transistors pass transistor based XOR gates with limitation of driving capability are reported in [14]. Various designs for XOR and XNOR gates using four transistors also presented in [7], [15], and [16]. Three inputs XOR design in place of two inputs is reported in [17]. XOR/XNOR design with ten transistors based on transmission gates is reported in [18]. XOR/XNOR circuits with dual feedback also reported in [19], [20].

At circuit level, an optimized design is necessary with reduced numbers of transistors, less power consumption and with adequate output voltage level. Here, in current work a new XOR gate with three transistors has been proposed. A new single bit full adder with 14 transistors based on proposed XOR gate and transmission gate multiplexer has been presented. The rest of paper is organized as follows: In Section II, a new 3 transistor XOR gate has been reported. Further, XOR/XNOR cell and a single bit full adder have been designed. In section III results of proposed single bit full adder designed in previous section have been presented and compared with earlier reported circuits. Section IV concludes the work.

### **II. SYSTEM DESCRIPTION**

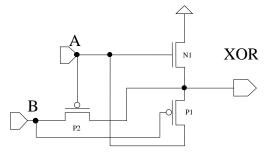

Proposed design for XOR with three transistors has been shown in Fig. 2. In proposed XOR, gate lengths of all three transistors have been taken as  $0.35 \,\mu\text{m}$ . Widths  $(W_n)$  of NMOS transistor (N1) has been taken  $0.5 \,\mu\text{m}$ . Width  $(W_p)$  for PMOS transistors (P1 & P2) have been taken as  $4 \,\mu\text{m}$ . In proposed circuit when A=B=0 output is low because P1 and P2 transistor are on and logic 0 is passed to output. With input combination of A=0 and B=1 circuit show high output as transistor P2 is on while transistors N1 & P1 are off and high logic is passed to output node. In another case when A=1and B=0, transistor P1 is on and high logic is passed to output node. In this case with A=1 transistor N1 also turns on and starts discharging the output node but the resistance of N1 has been made high by reducing its width. For acceptable output logic level for certain input combinations (W/L) ratios have been sized. Width of P1 and P2 has made large to reduce resistance while width of N1 is reduced for slow discharging. The voltage degradation due to threshold drop can be reduced by increasing W/L ratio of transistor of N1. The following equation [21] relates the threshold voltage with gate length and width of MOS transistor.

$$V_T = V_{T0} + \gamma \left( \sqrt{V_{SB} + \phi_0} \right) - \alpha_l \frac{t_{ox}}{L} \left( V_{SB} + \phi_0 \right) - \alpha_v \frac{t_{ox}}{L} V_{ds} + \alpha_w \frac{t_{ox}}{W} \left( V_{SB} + \phi_0 \right)$$

---(5)

where  $V_{t0}$  is the zero bias threshold voltage,  $\gamma$  is bulk threshold coefficient,  $\phi_0$  is 2  $\phi_F$  and  $\phi_F$  is Fermi potential,  $t_{ox}$  is the thickness of oxide and  $\alpha_1$ ,  $\alpha_v$  and  $\alpha_w$  are the process dependent parameters. From (5) it is apparent that by increasing the W it is possible to reduce the voltage degradation. In last case when A=B=1, output node show low logic as transistor N1 is on, so proposed circuit works as XOR gate.

Fig. 2. Design of proposed 3 transistor XOR gate

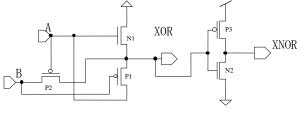

XNOR operation has been obtained with addition of inverter. Complete XNOR/XOR module with five transistors has been shown in Fig. 3 Width for P3 ( $W_p$ ) and N2 ( $W_n$ ) have been taken as 2.5 µm and 1.0 µm respectively.

Fig. 3. Design of proposed XNOR/XOR cell

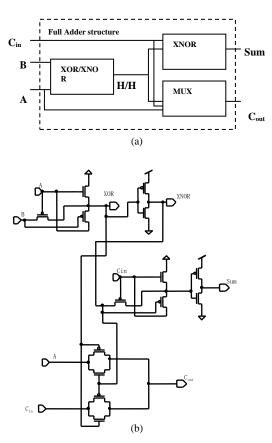

The full adder circuit can be implemented by various combinations of XOR/XNOR gates and multiplexer blocks. In present approach as shown in block diagram of Fig. 4 (a), we have used two XOR/XNOR cells and transmission gate multiplexer with four transistors to design the full adder.

Sum is generated by two XNOR gates as in equation (3) and Cout is generated by four transistor transmission gate multiplexer MUX as in equation (4). Two transistor multiplexers based on pass transistor logic can also be used to generate Cout which reduces the total transistor count of adder to 12. Since pass transistor logic shows poor noise margin so in current design transmission gate multiplexer approach has been utilized. For transmission gate multiplexer complementary gate control signals are required and in

current design both XOR and XNOR signals are already generated. The single bit full adder using proposed XOR/XNOR cell using 14 transistors has been implemented and shown in Fig. 4 (b). For multiplexer section values of width (Wn & WP) for NMOS and PMOS transistors have been taken as  $1.0 \,\mu\text{m}$  &  $2.5 \,\mu\text{m}$  respectively. Simulations also have been carried out with varying supply voltage from [3.3-1.8] V.

Fig. 4. Full adder using XOR/ XNOR gates and multiplexer (a) Block (b) Schematic diagram

# III. RESULTS AND DISCUSSIONS

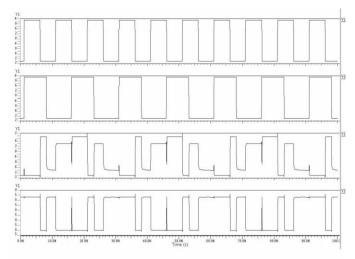

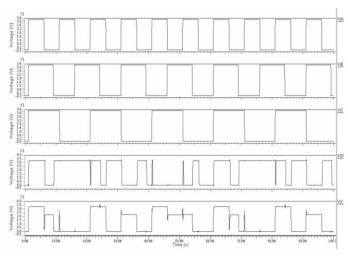

Simulations have been performed using SPICE based on TSMC 0.35 µm CMOS technology with supply voltage of 3.3V. Fig. 5 shows the input and output waveform results for proposed XOR and XNOR gate. Table-I shows minimum voltage level of high and maximum voltage level of low output signals for XOR and XNOR gate. Proposed XOR gate provide sufficient output voltage level and noise margin of approximately 2V with 3.3V input signals. Output voltage levels are improved with addition of inverter in XNOR gate with noise margin of approximately 3.2V and design show full swing operation.

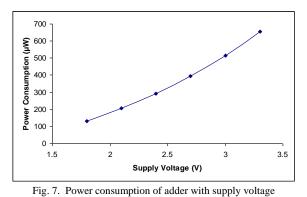

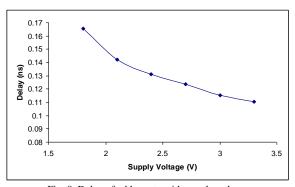

Table II shows power consumption, output delay, output voltage levels for sum and carry of proposed 14 transistors (14T) adder. Proposed adder show power consumption of 655.6149  $\mu$ W with maximum output delay of 0.11055ns. Noise margin of 3.2 V and 2.2V have been obtained for Sum and C<sub>out</sub> respectively with 3.3V power supply. Fig. 6 shows the input and output waveform results for proposed full adder circuit. Simulations also have been carried out with varying supply voltage to show its effects on power consumption & delay as shown in Table II. Fig. 7 show that power

consumption varies from [655.614-132.003]  $\mu$ W with variation in supply voltage from [3.3-1.8] V. Fig. 8 show that delay varies from [0.11055-0.1655270] ns with variation in supply voltage from [3.3-1.8] V. It has been observed from Fig. 7 and Fig. 8 that power consumption reduces whereas delay increase with reduction in supply voltage..

Adders reported in [3], [4], [8], [9], [11] have been simulated and comparison have been presented in Table-III. It has been shown that proposed adder show less power consumption as compared to TGA 20T [4], 22T HPSC [9] and 22T hybrid [8] adder with less number of transistors. Proposed circuit also show superiority in terms of transistor count as compared to 16T [11], 18T [3] adder with minor concession in power consumption.

Fig. 5. Input and out waveform for XOR/XNOR gates

TABLE I: OUTPUT LEVELS VARIATIONS WITH SUPPLY VOLTAGE FOR PROPOSED XOR AND XNOR GATE

|         | I KOI OSED MOK AND MIOK GATE |           |            |           |  |  |  |

|---------|------------------------------|-----------|------------|-----------|--|--|--|

| Supply  | Minimum                      | Maximum   | Minimum    | Maximum   |  |  |  |

| voltage | level for                    | level for | level for  | level for |  |  |  |

| (V)     | high XOR                     | low XOR   | high XNOR  | low XNOR  |  |  |  |

|         | output                       | output    | output (V) | output    |  |  |  |

|         | (V)                          | (V)       |            | (V)       |  |  |  |

| 3.3     | 2.402                        | 0.42      | 3.29       | 0.025     |  |  |  |

| 3.0     | 2.179                        | 0.42      | 2.99       | 0.1193    |  |  |  |

| 2.7     | 1.95                         | 0.40      | 2.69       | 0.00419   |  |  |  |

| 2.4     | 1.72                         | 0.40      | 2.39       | 000119    |  |  |  |

| 2.1     | 1.488                        | 0.40      | 2.09       | 0.00032   |  |  |  |

| 1.8     | 1.24                         | 0.40      | 1.79       | 0.00011   |  |  |  |

Fig. 6. Input and out waveform for proposed 14 transistor adder

| TABLE II: POWER CONSUMPTION, DELAY AND OUTPUT LEVELS   |  |

|--------------------------------------------------------|--|

| VARIATIONS WITH SUPPLY VOLTAGE FOR PROPOSED FULL ADDER |  |

| VARIATIONS WITH SUTTET VOLTAGE FOR TROFOSED FULL ADDER |        |        |        |        |        | IDDLK       |

|--------------------------------------------------------|--------|--------|--------|--------|--------|-------------|

| Supply<br>voltage<br>(V)                               | 3.3    | 3.0    | 2.7    | 2.4    | 2.1    | 1.8         |

| Power<br>consumpti<br>on<br>(µW)                       | 655.61 | 515.33 | 395.68 | 293.28 | 205.75 | 132.00<br>3 |

| Maximum<br>output<br>delay<br>(ns)                     | 0.11   | 0.11   | 0.12   | 0.13   | 0.14   | 0.16        |

| Minimum<br>level for<br>high sum<br>(V)                | 3.29   | 2.99   | 2.69   | 2.39   | 2.09   | 1.79        |

| Maximum<br>level for<br>low sum<br>(V)                 | 0.019  | 0.016  | 0.007  | 0.0026 | 0.0011 | 0.0009      |

| Minimum<br>level for<br>high Cout<br>(V)               | 2.21   | 1.98   | 1.74   | 1.50   | 1.25   | 1.01        |

| Maximum<br>level for<br>low Cout<br>(V)                | 0.0249 | 0.012  | 0.004  | 0.001  | 0.0005 | 0.0004      |

Fig. 8. Delay of adder gate with supply voltage

TABLE III: COMPARISONS OF PROPOSED FULL ADDER WITH EARLIER CIRCUITS

| Adder configuration     | Power consumption<br>(µW) | Number of transistors<br>for design |  |  |

|-------------------------|---------------------------|-------------------------------------|--|--|

| TGA20T [4]              | 1255.54                   | 20                                  |  |  |

| 16T adder [11]          | 591.07                    | 16                                  |  |  |

| 22T HPSC adder<br>[9]   | 1533.9                    | 22                                  |  |  |

| 18T [3]                 | 617.23                    | 18                                  |  |  |

| 22T hybrid adder<br>[8] | 1836.4                    | 22                                  |  |  |

| 14T [present work]      | 655.614                   | 14                                  |  |  |

# IV. CONCLUSIONS

In reported work a new design for XOR gate with three transistors is proposed and single bit full adder based on XOR/XNOR gates using 14 transistors has been designed. Proposed adder shows power consumption of  $655.614 \mu$ W and maximum output delay of 0.11055ns with supply voltage of 3.3V. Simulation results show that proposed adder works properly with reduced supply voltage up to 1.8 V and show power dissipation of 132.003  $\mu$ W with maximum delay of 0.1655270ns. Proposed adder also show adequate noise margin with reduced supply voltage. Adder has been compared with earlier reported circuits and show less power consumption with reduced transistor count than earlier reported circuits.

### REFERENCES

- [1] Y. Leblebici and S.M. Kang, *CMOS Digital Digital Integrated Circuits*, Singapore: Mc Graw Hill, India, 2nd edition, 1999.

- [2] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *IEEE J. Solid State Circuits*, vol. 32, no. 7, pp. 1079-1090, Jul. 1997.

- [3] N. Weste and K. Eshraghian, *Principles of CMOS VLSI Design*, A System Perspective, Addison-Wesley, 1993.

- [4] N. Zhuang and H. Wu, "A new design of the CMOS full adder," *IEEE J. Solid-State Circuits*, vol. 27, no. 5, pp. 840–844, May 1992.

- [5] Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung, "A novel multiplexer-based low-power full adder," *IEEE Transactions on Circuits and Systems: Express Briefs*, vol. 51, no. 7, Jul. 2004.

- [6] R. Shalem, E. John, and L. K. John, "A novel low-power energy recovery full adder cell," in *Proc. of Great Lakes Symp. VLSI*, Feb. 1999, pp. 380–383.

- [7] H. T. Bui, Y. Wang, and Y. Jiang, "Design and analysis of low-power 10-transistor full adders using XOR-XNOR gates," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process*, vol. 49, no. 1, pp. 25– 30, Jan. 2002.

- [8] S. Goel, A. Kumar, and M. A. Bayoumi, "Design of robust, energy –efficient full adders for deep sub micrometer design using hybrid-CMOS logic style," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol.14, no.12, pp.1309-1321, Dec. 2006.

- [9] M. Zhang, J. Gu, and C. H. Chang, "A novel hybrid pass logic with static CMOS output drive full-adder cell," *Proc. IEEE Int. Symp. Circuits Syst.*, May 2003, pp. 317-32.

- [10] C. K. Tung, Y. C. Hung, S. H. Shieh, and G. S. Huang, "A low-power high-speed hybrid CMOS full adder for embedded system," *IEEE conf.* on Design and Diagnostics of Electronic Circuits and Systems, 2007, pp.1-4.

- [11] A. M. Shams and M. Bayoumi, "A novel high-performance CMOS1-bit full adder cell," *IEEE Trans. Circuits Syst. II, Analog Digital Signal Process*, vol. 47, no. 5, pp. 478–481, May 2000.

- [12] A. M. Shams and A. Magdy, "A structured approach for designing low power adders," *Conference Record of the Thirty-First Asilomar Conference on Signals, Systems & Computers*, Nov. 1997, vol. 1, pp.757-761.

- [13] D. Radhakrishnan, "Low-voltage low-power CMOS full adder," Proc. IEE Circuits Devices Syst., Feb. 2001, vol. 148, pp. 19-24.

- [14] J. M. Wang, S. C. Fang, and W. S. Feng, "New efficient designs for XOR and XNOR functions on the transistor level," *IEEE J. Solid-State Circuits*, vol. 29, no. 7, pp. 780–786, Jul. 1994.

- [15] H. T. Bui, A. K. Al Sheraidah, and Y.Wang, "New 4-transistor XOR and XNOR designs," in *Proc. 2nd IEEE Asia Pacific Conf. ASIC*, 2000, pp. 25–28.

- [16] H. T. Bui, Y. Wang, and Y. Jiang , "Design and analysis of 10-transistor full adders using novel XOR–XNOR gates," in *Proc. 5th Int. Conf. Signal Process*, Aug. 21–25, 2000, vol. 1, pp. 619–622.

- [17] S. C. Fang, J. M. Wang, and W. S. Feng, "A new direct design for three-input XOR function on the transistor level," *IEEE Trans. Circuits System I: Fundamental theory and Applications*, vol. 43, no. 4, Apr. 1996.

- [18] A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 10, no. 1, pp. 20–29, Feb. 2002.

- [19] S. Goel, M. E. Elgamel, M. A. Bayouni, and Y. Hanafy, "Design methodologies for high-performance noise-tolerant XOR-XNOR circuits," *IEEE Trans. Circuits and Syst. 1*, vol. 53, no. 4, Apr. 2006.

- [20] Shiv Shankar Mishra et.al. "New design methodologies for high speed low power XOR-XNOR circuits," World Academy of Science, Engineering and Technology, vol.55, pp.200-206, 2009.

- [21] Y. Tsividis, Mixed Analog-Digital VLSI devices and Technology, Singapore: McGraw Hill, 1996.

**M. Kumar** received M. Tech. from Guru Nanak Dev University, India in 2003. He is an Assistant Professor in the Department of Electronics & Communication Engineering Department, Guru Jambheshwar University of Science & Technology, Hisar, India.. His research interests include low power CMOS system, Integrated circuit designs and microelectronics. He is a Life Member of IETE (India), ISTE (India) and member of Semiconductor Society of India.

Dr. Sandeep K. Arya is Associate Professor and Head in the Department of Electronics & Communication Engineering Department, Guru Jambheshwar University of Science & Technology, Hisar, India. He received M. Tech. and Ph.D degree from NIT Kurukshetra. He has more than 17 years of experience in teaching and research. His current area of research includes Optical Communication System, Integrated circuit Fabrication and CMOS circuit design. He has published more fifteen papers in referred international/national journals. He has also published more than twenty research articles in national and international conferences. He has completed project Up-gradation of Power Electronics and Industrial Control Laboratory, sponsored by MHRD, Govt. Of India at NIT Jalandhar, India

Dr. Sujata Pandey received the Masters degree in electronics (VLSI) from Kurukshetra University in 1994 and the Ph.D. degree from Department of Electronics, University of Delhi South Campus in Microelectronics in 1999. She joined Semiconductor Devices Research Laboratory, University of Delhi in 1996 under the Project of CSIR, Ministry of Science and Technology, Govt. of India. She joined Department of Electronics and Communication Engineering, Amity School of Engineering and Technology in 2002 as Assistant Professor. She is now Professor in the Department of Electronics and Communication Engineering, Amity University, Nodia, INDIA. She has published more than 40 research papers in International/National Journals/ Conferences. Her current research interest includes modeling and characterization of HEMTs, SOI Devices, and low power CMOS integrated circuit design. She is member of IEEE and Electron Device society.